## Agilent E2929A/B Opt. 200 PCI-X Performance Optimizer

## User's Guide

Agilent Technologies

### **Important Notice**

All information in this document is valid for both Agilent E2929A and Agilent E2929B testcards.

#### Copyright

© 2001 Agilent Technologies. All rights reserved.

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Agilent Technologies Inc. as governed by United States and international copyright laws.

Author: Anja Schauer, t3 medien GmbH

#### Notice

The material contained in this document is subject to change without notice. Agilent Technologies makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Agilent Technologies shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

## Contents

| Documentation Overview                               | 7  |

|------------------------------------------------------|----|

| PCI-X Performance Optimizer Overview                 | 9  |

| The Process of PCI-X Design                          | 10 |

| The Approach of the Performance Optimizer            | 11 |

| The PCI-X Performance Optimizer's User Interface     | 13 |

| Rules for Proper PCI-X Design                        | 15 |

| Running a Sample PCI-X Performance Optimizer Session | 17 |

| Test Example                                         | 18 |

| Loading the Setup File                               | 19 |

| Specifying the Completer Identification              | 20 |

| Specifying the Requester Identification              | 21 |

| Determining the Requester ID Number                  | 22 |

| Specifying the Requester-Completer Pair              | 23 |

| Specifying the Data Capture                          | 24 |

| Viewing the Test Results                             | 25 |

| Setting Up a Real-Time Performance Measurement Test  | 27 |

| Predefined Performance Measures                      | 28 |

| How to Select a Testcard for the Measurement         | 29 |

| How to Set Up the Testcard for the Measurement       | 29 |

| How to Select Predefined Performance Measures        | 32 |

| How to Set up Run Options                            | 33 |

| How to Run a Performance Measurement                 | 34 |

| Setting Up a PCI-X Performance Optimizer Test       | 37   |

|-----------------------------------------------------|------|

| Setting Up the Test Hardware                        | 38   |

| Requester Identification                            | 39   |

| Completer Identification                            | 39   |

| Preparing the Software for the Test                 | 40   |

| Setting up the Completer Identification             | 41   |

| Setting up the Requester Identification             | 42   |

| Selecting a Requester-Completer Pair                | 43   |

| Setting Up the Data Capture                         | 44   |

| Measuring System or Device Performance              | 47   |

| Running the Performance Measurements                | 48   |

| Interpreting the Result Charts                      | 49   |

| PCI-X Usage                                         | 50   |

| Burst Usage                                         | 5    |

| Command                                             | 52   |

| Latency                                             | 53   |

| Interpreting the Report Output                      | 54   |

| Using the Report Output for Performance Evaluation  | 55   |

| General Information on the System under Test        | 56   |

| Analyzing the PCI-X Throughput                      | 57   |

| Analyzing the PCI-X Utilization                     | 58   |

| Analyzing the PCI-X Efficiency                      | 59   |

| Analyzing the Split Behavior                        | 60   |

| The Bus Users Overview                              | 61   |

| Summary for the Performance Evaluation Example      | 62   |

| Using the Report Output for Performance Optimizatio | n 62 |

| Analyzing the Bus Utilization                       | 63   |

| Analyzing the Traffic Overhead                      | 64   |

| Analyzing the Byte Enable and Burst Behavior        | 65   |

| Analyzing the Bursts                                | 66   |

| Analyzing Command Termination                       | 69   |

| Summary of the Performance Optimization Example     | 71   |

| ſ | ^ | n | ÷ | ^ | n | ts |  |

|---|---|---|---|---|---|----|--|

| U | υ | ш | U | C | Ц | เอ |  |

| Reusing the Tes  | t Setups and Results                            | 73  |

|------------------|-------------------------------------------------|-----|

|                  | Printing and Exporting Test Results             | 74  |

|                  | Printing the Test Results                       | 74  |

|                  | Exporting the Report                            | 75  |

|                  | Exporting the Trace Memory                      | 75  |

|                  | Saving the Test Settings                        | 76  |

|                  | Reusing Previously Saved Data                   | 76  |

| Going Further Ir | ito Details                                     | 79  |

|                  | Verifying Good Performance                      | 79  |

|                  | Performance in the Presented Charts             | 80  |

|                  | Identifying Design Rule Violations              | 81  |

|                  | Replacing Cards or Improving Behavior           | 82  |

|                  | Improving Completer Behavior                    | 83  |

|                  | Minimize First Word Latencies                   | 83  |

|                  | Command Termination                             | 84  |

| Report Referend  | ce                                              | 87  |

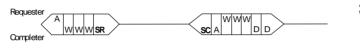

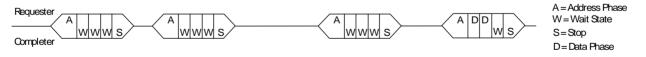

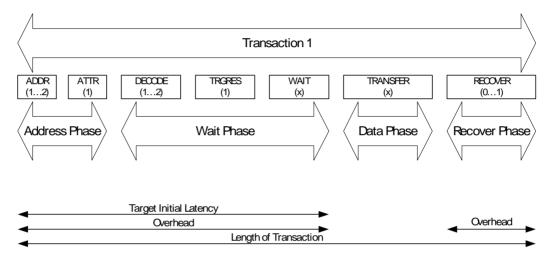

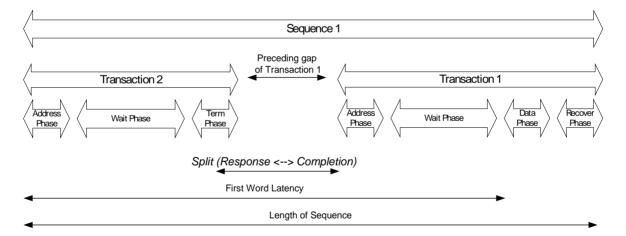

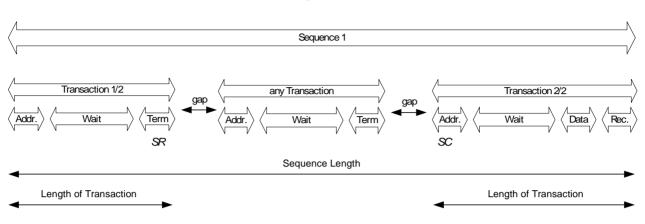

|                  | Typical PCI-X Transactions and Sequences        | 88  |

|                  | Example Transfers                               | 90  |

|                  | Bus Statistics (Report Sections 1 to 7)         | 92  |

|                  | General Information (Report Section 1)          | 93  |

|                  | Test Base (Report Subsection 1.1)               | 93  |

|                  | Statistical Base (Report Subsection 1.2)        | 94  |

|                  | Invalid Measures (Report Subsection 1.3)        | 96  |

|                  | Basic Bus Statistics (Report Section 2)         | 97  |

|                  | Bus Throughput Statistics (Report Section 3)    | 98  |

|                  | Efficiency Statistics (Report Section 4)        | 99  |

|                  | Bus Utilization Statistics (Report Section 5)   | 101 |

|                  | Bus Users Overview (Report Section 6)           | 102 |

|                  | Split Transaction Statistics (Report Section 7) | 103 |

| Requester-Completer Pair Measurements                                              |       |

|------------------------------------------------------------------------------------|-------|

| (Report Section 8)                                                                 | 104   |

| The Header of Report Section 8                                                     | 105   |

| Statistical Basis (Report Subsection 8.1)                                          | 105   |

| Bus Utilization (Report Subsection 8.2)                                            | 106   |

| Data Phase (Report Subsection 8.2.1)                                               | 107   |

| Overhead (Report Subsection 8.2.2)                                                 | 109   |

| Command Usage, Observed per Sequence<br>(Report Subsection 8.2.3)                  | 111   |

| Command Termination, Observed per Transactions<br>(Report Subsection 8.2.4)        | 112   |

| Byte Count over Command, Observed per Sequence<br>(Report Subsection 8.2.5)        | 114   |

| Byte Count over Command, Observed per Transaction<br>(Report Subsection 8.2.6)     | 116   |

| Efficiency Statistics (Report Subsection 8.3)                                      | 117   |

| Efficiency over Byte Count, observed per Sequence                                  |       |

| (Report Subsection 8.3.1)                                                          | 118   |

| Termination Statistics (Report Subsection 8.4)                                     | 119   |

| Split Statistics (Report Subsection 8.4.1)                                         | 119   |

| Termination Burst Histogram, Observed per Transaction<br>(Report Subsection 8.4.2) | 120   |

| Latency Histogram, Observed per Sequence                                           |       |

| (Report Subsection 8.5)                                                            | 121   |

| Top Ten List of First Word Latencies (Report Subsection 8 122                      | .5.1) |

| Definitions of Used Measures                                                       | 125   |

## **Documentation Overview**

This section shows you the different types of documents offered by Agilent Technologies and gives you an overview of which documents are available when you work with the Agilent E2929A/B PCI-X Exerciser and Analyzer.

All documents are valid for both Agilent E2929A and Agilent E2929B testcards. The following documents are available:

#### Getting Started Guide • Getting Started Guide

Introduces standard analysis features and provides an example of how to set up the protocol observer.

This guide also gives detailed information about the hardware and interfaces.

#### User's Guides • Agilent E2929A/B Opt. 300 PCI-X Exerciser User's Guide

Provides information on programming the testcard as an initiator and/or target device. It shows you how to actively stimulate the PCI-X bus.

This guide shows how to:

- Initiate data transfers on the PCI-X bus (act as requester-initiator).

- Act as completer-target.

- Handle split completion transactions (act as completer-initiator).

- Handle open requests (act as requester-target).

- Agilent E2929A/B Opt. 100 PCI-X Analyzer User's Guide

Provides information on how to examine the behavior of a PCI-X device on the bus and shows how to perform functional tests such as data compares.

• Agilent E2929A/B Opt. 200 PCI-X Performance Optimizer User's Guide

Provides all features that are needed to evaluate and optimize any device under test in terms of the performance.

**GUI and C-API/PPR References**

#### • Agilent E2929A/B Windows and Dialog Boxes Reference

Provides reference information on all windows and dialog boxes of the Agilent E2920 graphical user interface (GUI).

• Agilent E2929A/B Opt. 320 C-API/PPR Reference

Describes all C functions, types and definitions of the application programming interface of the Agilent E2929A/B PCI-X testcard.

This reference also provides the commands and abbreviations that are used in the command line interface (CLI) of the graphical user interface.

## PCI-X Performance Optimizer Overview

The Agilent E2929A/B Opt. 200 PCI-X Performance Optimizer is an additional option available for the Agilent E2920 verification tools series. Its complete integration into the framework lets it be used directly with a PCI-X Exerciser and Analyzer testcard and its graphical user interface (GUI).

The Performance Optimizer provides all the features that are needed to evaluate and optimize any device under test in terms of the performance. This includes the devices on the PCI-X bus as well as the complete PCI-X system. For this purpose, the software defines and calculates performance measures such as efficiency, data throughput, bus utilization or split behavior, which allow you to compare and communicate the test results.

With these features, you can easily reveal which devices cause lower performance in the system under test. Furthermore, you can examine the data traffic of every device in detail to track down the exact cause for the unsatisfactory performance.

With the information provided by the software, you can improve your system either by selecting components with better performance or by debugging or redesigning the affected devices.

## **The Process of PCI-X Design**

Due to the complex PCI-X protocol, there are many ways to improve PCI-X performance, both on a component level as well as on a system level.

Even when all the rules included in the PCI-X specifications are followed, the performance of your device still depends on many factors.

The PCI-X performance optimizer is a powerful tool in the following cases:

- you are designing a chip or an add-in card,

- you are integrating a system and you need to select between different components on the market,

- you are adjusting system and device parameters in order to optimize the overall performance.

For all imaginable tasks, it is essential to evaluate the quality of the different devices in your system under test. Furthermore, it is important to document your results and to communicate them to colleagues or other companies.

These facts raise the question for a powerful, yet easy-to-use solution to find the bottlenecks in your system. If you manage to identify the part that decreases the system performance due to its poor design, you know what to improve or replace. Eventually, this process will lead to significantly more powerful PCI-X systems.

## The Approach of the Performance Optimizer

| Methods for Performance Analysis | Basically, there are two different approaches to analyze a system under<br>test. Which approach should be used depends on the particular case.<br>With the Agilent E2929A/B Performance Optimizer, you can employ both<br>approaches for performance analysis:                                                                                                                                                                                                                                                                             |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  | Real-Time Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                  | Real-time performance analysis based on programmable counters allows<br>long-term observation of the system's properties like latencies, etc. This<br>method provides valuable information over long time periods about what<br>the general performance of your system is. It is limited, however, in its<br>ability to provide meaningful information to track down the root cause of<br>performance issues.                                                                                                                              |

|                                  | Post-Processed Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                  | The post-processed analysis is based on one or more recorded traffic traces in the trace memory. This allows a detailed analysis of all performance aspects like bus utilization, command usage, efficiency, or split statistics.                                                                                                                                                                                                                                                                                                          |

|                                  | The observation time, however, is limited due to the large amount of data that is stored.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Recording Traffic Samples        | The traffic is recorded in the trace memory of the PCI-X Exerciser and<br>Analyzer card. A set of values in the trace memory is referred to as a<br>traffic sample. One traffic sample can be recorded for every clock cycle.<br>However, if a sequence of clock cycles occurs on the bus without any<br>changes in the relevant bits, for example, idle states, they are stored as<br>one sample. This behavior extends the possible observation time and,<br>thus, yields better measurement results based on a larger statistical base. |

| Trace Memory Size                | The trace memory of the Agilent E2929A/B testcard can store up to 2M traffic samples. One sample here is referred to as a sequence of clock cycles without any changes in the bits that are significant for the performance.                                                                                                                                                                                                                                                                                                               |

The Steps of PerformanceThe Agilent E2929A/B PCI-X Performance Optimizer performs the dataOptimizationanalysis by taking the following steps:

• Recording the bus traffic

The measurement is either started by the user or can be set up to be triggered when a certain event occurs on the bus. The trace memory then records the data until the trace memory is full or until another specified bus event occurs on the bus.

Usually, the observation time is only a split-second. Thus, the memory content is a "snapshot" of the bus activities.

• Analyzing the recorded data

For the analysis, the trace memory content is loaded from the testcard into the PCI-X Performance Optimizer. The software then derives a large number of result values from the sampled bus activities.

• Presenting the test results

The Performance Optimizer outputs the results of the analysis in graphical charts and in a textual report. This report is arranged according to the requirements of system and device evaluation and optimization.

These test results give a detailed look into your system's and devices' traffic behavior. You can identify the devices with poor performance and get detailed hints for improvement.

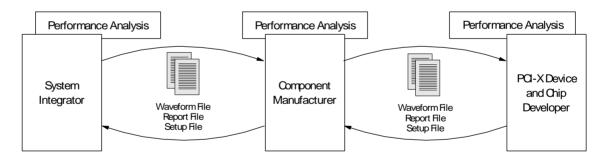

• Generating result files (setup file, report file, and waveform file) Optionally, you can store your test settings and test results in files. With these files, you can reuse the settings or the data from previous settings. They also provide a good method for analyzing the devices in workgroups. The report file holds the results of the post-processed analysis in textual form, the waveform file holds the trace memory contents. The setup file with the test settings can be used to reproduce the test environment.

## The PCI-X Performance Optimizer's User Interface

The Agilent E2920 Series software provides two different User Interfaces for real-time performance and post-processed measurements.

### **Real-Time Performance Analysis**

The User Interface for performing real-time performance analysis is available via a separate GUI, which can be accessed by selecting:

Start > Programs > Agilent E2920 PCI-X > PCI-X Real Time

Performance GUI

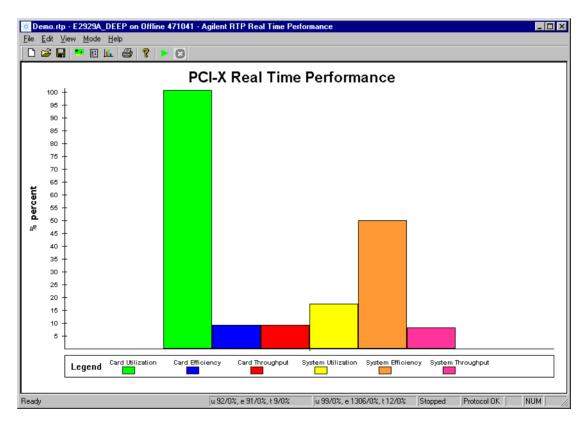

The user interface for the real-time performance measurements looks as follows:

**Navigation** The most important features of the real-time performance measurement are available via the buttons in the tool bar. All these features and more are available via the menus, as well.

### **Post-Processed Performance Analysis**

The User Interface for performing post-processed performance analysis is fully integrated into the framework of the Agilent E2929A/B Exerciser and Analyzer. All its windows and controls appear as additional features of the GUI that is assumed to be known from the PCI-X Exerciser and Analyzer software.

**Navigation** The most important features of each part of the framework are available via the buttons in the respective button group. All these features and more are available via the menus of the main window, as well.

Performance Button GroupYou can quickly open the windows providing the features of the PCI-XPerformance Optimizer with the Performance buttons.

**Performance Windows** Within the PCI-X Performance Optimizer, the following windows are provided for performance analysis and optimization:

• Performance Setup

In the Performance Setup window, you can set up the contents of the report to be generated, identify the requester and completer devices to be considered in the test, and control the data capture for the performance analysis.

Performance Report

The performance report lists all results in a hierarchical way, so that you can focus on different levels of detail.

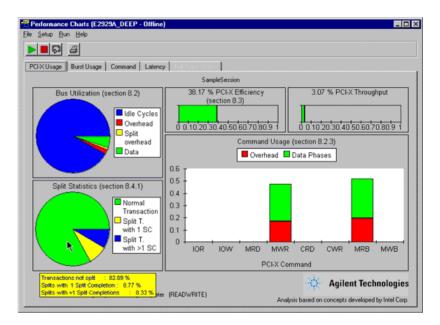

• Performance Charts

The performance charts show results of the analysis of the captured PCI-X traffic.

## **Rules for Proper PCI-X Design**

When designing PCI-X devices, a lot of design rules need to be obeyed to avoid device conflicts. Furthermore, there are rules that need to be followed to improve the communication abilities of the devices. Designing the devices so that they behave according to these rules ensures that the device will not only result in good performance in a test environment, but on all platforms and under most circumstances.

Even when all these rules have been followed, the design with the best performance still depends on the type of the device and its dedicated tasks. Hence, a fair amount of design experience is likely to yield better results.

This document can only name a few rules that are essential for good performance:

• Use long bursts.

On most platforms, read bursts should have a minimum length of 64 dwords for reasonable performance. Write bursts should have a minimum length of one cacheline.

• Use memory commands, avoid I/O commands.

I/O commands can stress the processor. Although the PCI-X bus performance might not be directly affected, the use of I/O commands reduces the performance of the whole system by using CPU time.

Use split transactions to relieve the bus.

If the target signals a split response, the bus can be used by other initiators to transfer data.

These are only a few basic rules that should always be respected. More hints for identifying poor designs and for improving the performance are given in "Going Further Into Details" on page 79.

## Running a Sample PCI-X Performance Optimizer Session

The following sections show how to set up a performance measurement with the Agilent E2929A/B Performance Optimizer Graphical User Interface (GUI), by means of an example.

The recommended approach is:

- 1. Specifying the identification of the devices under test In detail that means:

- Identify the completer devices by its address ranges.

- Identify the requester devices by its bus, device and function numbers.

- Select the device pair, the test is to be focussed on.

- 2. Setting up the data capture

Define the start and the duration of the test.

3. Viewing the test results

Analyze the data traffic that is recorded in the trace memory after the test has finished.

### **Test Example**

In a PCI-X bus system with 64-bit bus width and 33-MHz bus speed, both the performance of the whole system and of a particular requestercompleter pair is to be evaluated.

| <b>Requester Identification</b> | The requester device named <i>MyRequester</i> has the following |

|---------------------------------|-----------------------------------------------------------------|

|                                 | identification:                                                 |

| ٠ | bus number:      | ab∖h |

|---|------------------|------|

| • | device number:   | l∖h  |

| • | function number: | 0\h  |

| <b>Completer Identification</b> | The completer device named <i>MyCompleter</i> has the following |

|---------------------------------|-----------------------------------------------------------------|

|                                 | identification:                                                 |

|                                 | • have addresses (0000) h                                       |

| • | base autress. | 40000\11 |

|---|---------------|----------|

| ٠ | size:         | 5000\h   |

The performance measurement should not be restricted on any commands.

- **Requester-Completer Pair** The performance measurement has to focus on the traffic between *MyRequester* and *MyCompleter*. All types of commands are of interest for the measurement.

- **Data Capture** The data capture has to start immediately and stop after 200000 samples have been recorded.

- Viewing the Results When you view the results in the performance charts, you get quick access to the performance of your system and your device under test.

### Loading the Setup File

When preparing the Agilent E2929A/B Performance Optimizer for a test session, you do not necessarily need to load a setup file. The setup file for the example measurements, however, is included in the software package.

To set up your application for the example test, follow the instructions below:

- 1 Select *Load* from the *File* menu in the main window.

- 2 Select the file SampleSession.bst.

- **3** Click the *Load* button.

The setup file assumes an Agilent E2929A/B\_Deep testcard is to be used for the test—at least in offline/demo mode. If this is not the case, you will be informed in a message box. Change the configuration to the testcard required for the example.

After you have loaded the setup file, the test measurements can be started. However, we need to verify the correctness of the settings. Therefore, we go through the setup step-by-step and make changes where applicable.

### **Specifying the Completer Identification**

In order to enable the Agilent E2929A/B PCI-X Performance Optimizer to identify particular devices communicating on the PCI-X bus, you need to specify them in the setup. Requesters are identified by their bus, device and function numbers, completers by their address range.

To specify the completer:

1 Select the *Performance Setup* item from the *Performance* menu.

The Performance Setup window opens, displaying the *Completer Identification* tab.

2 Enter a name, the base address, the size and the commands considered in the measurements for a particular completer. You can specify up to ten different completer devices.

In this example, MyCompleter is specified as shown below.

| <u>Run H</u> elp |                           |                                 |                      |         |   |

|------------------|---------------------------|---------------------------------|----------------------|---------|---|

| oort Completer   | Identification   Requeste | er Identification 🗍 Pair Select | Capture              |         |   |

|                  |                           | Enter Address and Size for C    | Completers           |         |   |

|                  | Completer Name            | Base Address                    | Size                 | Command |   |

| Completer_1      | MyCompleter               | 0000000000040000\h              | 0000000000005000\h   | ANY     |   |

| Completer_2      | Completer_2               | 0000000000000000\h              | 00000000000000000\h  | NONE    |   |

| Completer_3      | Completer_3               | 0000000000000000\h              | 00000000000000000\h  | NONE    |   |

| Completer_4      | Completer_4               | 0000000000000000\h              | 00000000000000000\h  | NONE    |   |

| Completer_5      | Completer_5               | 0000000000000000\h              | 00000000000000000\h  | NONE    |   |

| Completer_6      | Completer_6               | 0000000000000000\h              | 00000000000000000\h  | NONE    |   |

| Completer_7      | Completer_7               | 0000000000000000\h              | 00000000000000000\h  | NONE    |   |

| Completer_8      | Completer_8               | 0000000000000000\h              | 00000000000000000\h  | NONE    |   |

| Completer_9      | Completer_9               | 0000000000000000\h              | 00000000000000000\h  | NONE    |   |

| Completer_10     | Completer_10              | 0000000000000000\h              | 000000000000000000\h | NONE    | • |

### **Specifying the Requester Identification**

To view the requester identification:

- **1** Select the *Requester Identification* tab in the Performance Setup window.

- 2 Enter the bus, device and function number for a particular requester.You can specify up to ten different requester devices.

In this example, *MyRequester* is specified as shown below.

| <u>Bun H</u> elp |                |                                                       |        |          |   |

|------------------|----------------|-------------------------------------------------------|--------|----------|---|

| port Completer I |                | r Identification Pair Sel<br>us-, Device- and Functio |        | ters     |   |

|                  | Requester Name | Bus                                                   | Device | Function |   |

| Requester_1      | MyRequester    | ab\h                                                  | 1\h    | 0\h      | 4 |

| Requester_2      | Requester_2    | 0\h                                                   | 0\h    | 0\h      |   |

| Requester_3      | Requester_3    | 0\h                                                   | 0\h    | 0\h      |   |

| Requester_4      | Requester_4    | 0\h                                                   | 0\h    | 0\h      |   |

| Requester_5      | Requester_5    | 0\h                                                   | 0\h    | 0\h      |   |

| Requester_6      | Requester_6    | 0\h                                                   | 0\h    | 0\h      |   |

| Requester_7      | Requester_7    | 0\h                                                   | 0\h    | 0\h      |   |

| Requester_8      | Requester_8    | 0\h                                                   | 0\h    | 0\h      |   |

| Requester_9      | Requester_9    | 0\h                                                   | 0\h    | 0\h      |   |

|                  | Requester_10   | 0\h                                                   | 0\h    | 0\h      |   |

### **Determining the Requester ID Number**

If you need to know the bus, device and function number of a particular requester, use the Performance Report.

**NOTE** The following procedure can only be performed in online mode.

To determine the requester ID number:

- **1** Select *Performance Report* from the *Performance* menu in the application's main window to open the Performance Report window.

- 2 Run the performance measurement.

The performance software does a configuration scan on the whole PCI-X bus system and presents the results in the report file. Subsection 1.1 of the report lists all requesters found on the bus and displays their corresponding bus, device and function numbers.

| Performance Report 📃 🗆 🗙                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| jile <u>S</u> etup <u>R</u> un <u>H</u> elp                                                                                                                                           |

|                                                                                                                                                                                       |

| E2929A PCI-X Performance Analyzer - Report File                                                                                                                                       |

| Agilent Technologies PCI-X Performance Analyzer SW (Vers. 01010000)<br>Analysis based on concepts developed by Intel Corporation<br>Statistical Report File<br>Date: 02/12 at 12:30 h |

| 1 GENERAL INFORMATION                                                                                                                                                                 |

| 1.1 Test Base                                                                                                                                                                         |

|                                                                                                                                                                                       |

| Bus Speed                                                                                                                                                                             |

| 2. >Req_1 Bus:Oxab Dev:OxO1 Func:OxO0                                                                                                                                                 |

| 3. >Req_2 Bus:0xab Dev:0x02 Func:0x00                                                                                                                                                 |

| legend:<br>! = Requester defined by user and found in trace<br>? = Requester defined by user and not found in trace<br>> = New Requester found on bus                                 |

|                                                                                                                                                                                       |

The desired bus, device and function numbers can now be entered in the *Requester Identification* tab of the *Performance Setup* window.

### **Specifying the Requester-Completer Pair**

The setup of the performance test allows you to focus the performance measurement on the traffic of particular devices. Furthermore, the performance optimizer software allows to determine which transfer types (read, write or both) are of interest in your observation.

To specify the requester-completer pair:

- 1 Select the *Pair Select* tab in the Performance Setup window.

- **2** Select the requester and the completer from the lists and determine to which command typs the measurement is restricted (Read, Write or both).

In this example, the measurement is focussed on *MyRequester* and *MyCompleter* and the type of command is not restricted.

| 🖑 Performance Setup 📃 🗖                                                      | x |

|------------------------------------------------------------------------------|---|

| <u>File R</u> un <u>H</u> elp                                                |   |

|                                                                              |   |

| Report Completer Identification Requester Identification Pair Select Capture |   |

| Select the Requester Completer Pair you want to observe                      |   |

| Requester MyRequester                                                        |   |

| Completer: MyCompleter                                                       |   |

| Command Type: Read Write                                                     |   |

| Title: SampleSession                                                         |   |

|                                                                              |   |

### **Specifying the Data Capture**

You can set up the performance test not only to focus on the traffic of particular devices, you can also control the start and the duration of the test.

For controlling the start, you can define a particular event that triggers the data capture. For controlling the duration of the test, you can determine the amount of samples to be recorded or specify a particular event that stops data recording.

To specify the data capture:

- 1 Select the *Capture* tab in the Performance Setup window.

- **2** Specify a trigger for the start of the performance measurements and define the duration of the test.

In this test example, the data recording starts immediately. The test stops as soon as the trace memory is filled with 200000 samples.

| 🖑 Performance Setup                                                          |      |

|------------------------------------------------------------------------------|------|

| <u>File R</u> un <u>H</u> elp                                                |      |

|                                                                              |      |

| Report Completer Identification Requester Identification Pair Select Capture |      |

| Trigger on                                                                   |      |

| TRUE                                                                         | Edit |

|                                                                              |      |

| End of Analysis                                                              |      |

| Stop at end of Tracememory                                                   |      |

| Stop after 200000 samples                                                    |      |

| O Stop after access to address 0 with IO Read                                |      |

|                                                                              |      |

|                                                                              |      |

|                                                                              |      |

|                                                                              |      |

|                                                                              |      |

|                                                                              |      |

|                                                                              |      |

|                                                                              |      |

### **Viewing the Test Results**

The results of the performance tests can be viewed in different ways. For instance, there is the Performance Charts window, that displays the test results in several charts. Another way is the performance report.

1 In the application's main window, select *Performance Charts* from the *Performance* menu to open the Performance Charts window.

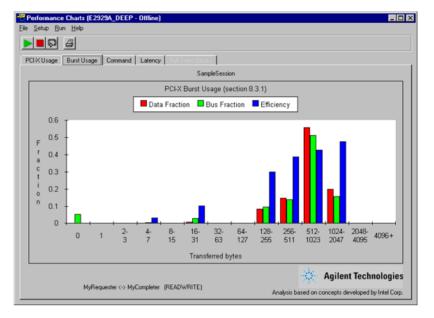

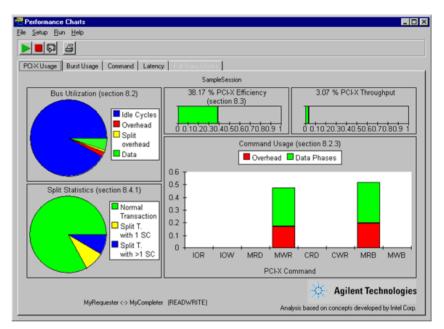

This window presents the performance of your system under test on five different tabs. The *PCI-X Usage* tab (as shown above) presents general traffic statistics such as bus utilization, the PCI-X command usage and the split behavior.

**2** Move the mouse over either pie chart to view the numerical values of the various pie slices. The values are shown as screen tips.

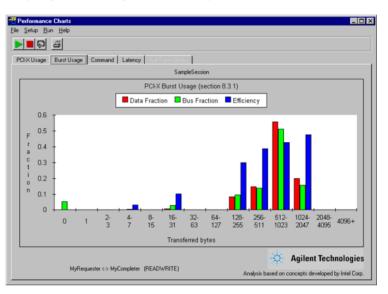

**3** Switch to the *Burst Usage* tab.

This tab displays detailed information on the distribution of the data phases and the overhead over the different burst lengths in the traffic.

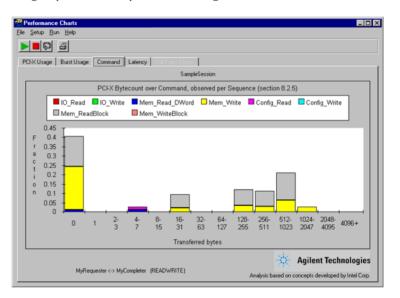

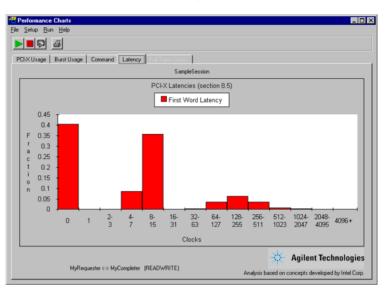

**4** Switch through the different tabs to get an overview of the provided information.

Loading the Example Test Results For convenience, the results of the example test also are included in the software package. To view these results, do the following steps:

- In the Performance Charts window, select *Load* from the *File* menu.

A message box appears, informing you that the selected action might take a few minutes to complete.

- **2** Click the *Continue* button to open the file dialog box.

- **3** In the file dialog box, select the file *SampleSession.wfm* in the path *samples/demo/* and click the *Load* button.

After the loaded data is analyzed, the results are displayed in the Performance Charts window and the other windows of the Performance Optimizer.

**NOTE** This example waveform file was produced on a 64-bit system using an Agilent E2929A/B\_Deep PCI-X testcard. Thus, to successfully load it into the GUI, the bus width and the hardware need to be set up the same way.

If your software is set up differently, a message box informs you. Change the hardware settings and repeat the procedure above.

## Setting Up a Real-Time Performance Measurement Test

In the bring-up and debug phase of a PCI-X device or a system (containing PCI-X bus and PCI-X devices), you need to evaluate the performance of the device or system under test.

The Agilent PCI-X E2920 software supports real-time performance measurement by providing predefined, standardized performance measurements, such as PCI-X efficiency and PCI-X utilization.

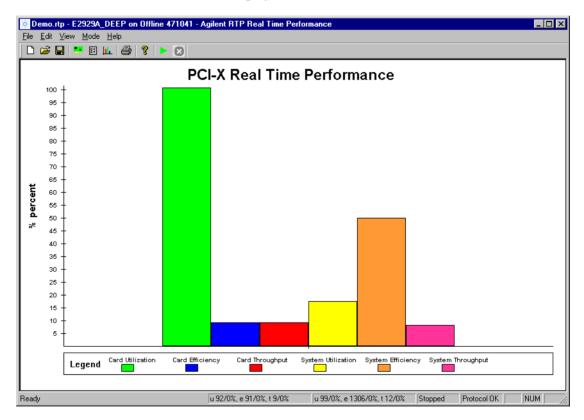

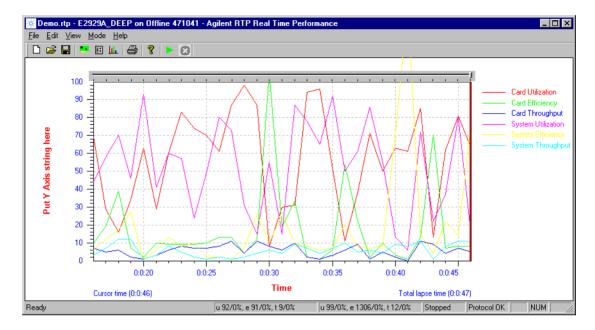

These measures can be set up easily. The results are shown in the main window of the RTP GUI.

The performance measurement is based on counting certain events on the PCI-X bus. For the predefined measurements, the counters are set up automatically.

The PCI-X Performance Optimizer (option #200) expands the possibilities of real-time performance measurements, by providing means for detailed post-processed analysis.

**Generating PCI-X Traffic** The PCI-X Analyzer can measure any kind of PCI-X traffic, regardless of how it was generated. However, it is useful to generate traffic in a controlled way for reproducibility in case of troubleshooting or root cause analysis.

Typically, you will use benchmark tests to generate traffic for this purpose.

## **Predefined Performance Measures**

For real-time performance measurements, the PCI-X Analyzer counts occurrences of predefined events or sequences of events on the PCI-X bus. The results are derived and displayed in real time.

Available Measurements The following predefined measures are provided:

#### • Throughput

Throughput is the amount of transferred data per time. It is measured in Mbyte per second. When running a real-time measurement, this value is displayed in percent of the maximum value (for 133-MHz/64-bit systems: 1014 Mbyte per second).

The maximum value can vary between 132 MByte/s in a 33 MHz/32-bit system, 528 MByte/s in a 66 MHz/64-bit system and up to 1014 MByte/s in a 133 MHz/64-bit system.

#### • Utilization

Utilization measures the relation between busy bus time and total bus time during a transfer.

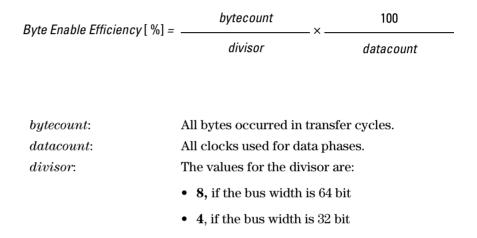

#### • Efficiency

Efficiency is a measure of how well the bus is used. It is the most important value when considering PCI-X performance.

The efficiency of a transfer is the relation between the amount of data that was *really* transferred and the amount of data that *could* have been transferred by the used cycles of that transfer (busy clocks).

Efficiency is derived from throughput and utilization. An efficiency near 100 % means that a device made best use of the time it occupied the bus (utilization) by transferring as much data as possible during that time frame (high throughput).

#### Retry Rate

This is the ratio between transactions terminated by retry and all terminations.

#### • Split Rate

This is the ratio between transactions terminated by split and all terminations.

# How to Select a Testcard for the Measurement

To select a testcard:

**1** Select *Select Testcard*... from the *Edit* menu.

This open the RTP Select Testcard window.

| ard Name   | Model       | Port    | Num |

|------------|-------------|---------|-----|

| Testcard 1 | E2929A_DEEP | Offline | 471 |

| Testcard 2 | E2929A_DEEP | Offline | 471 |

| Testcard 3 | E2929A_DEEP | Offline | 471 |

| Testcard 4 | E2929A_DEEP | Offline | 471 |

|            |             |         | •   |

2 Click onto the testcard you need for the performance measurement. The selected testcard can be specified in the RTP Testcard Setup window.

# How to Set Up the Testcard for the Measurement

To view the settings of the available testcards:

♦ Select *Setup Testcard*... from the *Edit* menu.

| TP Testcard Sel                          | up                                                                                                             | ×      |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------|

| ─ Testcard Setup ─<br>─ 1. Testcard info |                                                                                                                | OK     |

|                                          |                                                                                                                | Cancel |

| Name:                                    | Testcard 1                                                                                                     |        |

| Port:                                    | Offline                                                                                                        |        |

| Port Number:                             | 471041                                                                                                         |        |

| Serial Number:                           | UniqueID                                                                                                       |        |

| Model Number:                            | E2929A_DEEP                                                                                                    |        |

| 2. Location/Bu                           | s info                                                                                                         |        |

| Location:                                | Unknown                                                                                                        |        |

| Bus Speed:                               | 133.33 MHz Bus Width: 64                                                                                       |        |

| <u>3</u> . Settings                      |                                                                                                                |        |

| Use Protoco                              | ol Checker (Rule <u>M</u> asking)                                                                              |        |

| 🔲 🔲 Use Analyz                           | er in the second se |        |

| Trigger I                                | /0 Lines                                                                                                       |        |

| Upload 1                                 | Trace on Trigger                                                                                               |        |

| File:                                    | Browse                                                                                                         |        |

|                                          |                                                                                                                |        |

This open the RTP Testcard Setup window.

You can modify all current testcard settings under *Settings*. Here you can enable and disable card features (protocol checker and analyzer features).

- **Features** The testcard's Analyzer part includes the protocol observer and trigger in/out capabilities.

- Protocol Checker

The testcard's protocol checker continuously monitors the bus and checks for violations of predefined protocol rules, which are partly defined by the PCI-X specification and partly by Agilent. Each individual rule can be masked out. In this case, it neither triggers the trace memory, nor appears in the report. To mask rules, click the details button next to the *Use Protocol Checker (Rule Masking)* check box.

#### • External/Cross Triggering

To facilitate triggering of external measurement devices, and to trigger other testcards in the system for a *snapshot* whenever an error occurs, the testcards are set up to use the external trigger lines that must be connected to reflect their internal triggering state. Whenever the testcard's trace memory triggers, a trigger-out signal is generated. All trigger-in lines are monitored and used to trigger the card's trace memory.

Which trigger-out line is used for triggering is determined by the testcard's bus number. Therefore, only one testcard per bus needs to be used for cross-triggering.

To find out which trigger-out line is used, use the following formula:

triggerline := bus number MOD 12

#### **Example:**

bus number is 16 -> trigger line is 4; bus number is 5 -> trigger line is 5; ...

For further information on testcard settings, refer to *RTP Setup Testcard Window* in the *Agilent E2929A/B Windows and Dialog Boxes User Interface Reference*.

### How to Select Predefined Performance Measures

The Agilent E2920 Performance software can calculate two real-time measures simultaneously. The test results are displayed side by side on screen.

To select the predefined performance measures to be used:

1 From the Edit menu, select Setup Measurement....

| leasureme   |                                  |  |

|-------------|----------------------------------|--|

| Card Perf   | ormance                          |  |

| Efficie     | ency, Throughput, Utilization    |  |

| 🔲 Retry     |                                  |  |

| 🔲 Split     |                                  |  |

| Sustem P    | 'erformance                      |  |

|             |                                  |  |

|             | ency, Throughput, Utilization    |  |

| 🗖 Retry     |                                  |  |

| 🔲 Split     |                                  |  |

| Mived Ca    | rd/System                        |  |

|             | •                                |  |

| Card        | Utilization & System Utilization |  |

|             |                                  |  |

| )nly two cł | hecks at a time are permitted    |  |

- **2** Check the predefined measurements to be calculated and displayed for card performance, system performance or both.

- **NOTE** You can only run two measurements at one time.

The settings will be used the next time you start a performance measurement.

### How to Set up Run Options

To set up run options:

1 Open the RTP Options dialog box by selecting *Options*... from the *View* menu.

| RTP Options                                                                                                                                  | ×            |

|----------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Measure<br>Update Interval (ms): 250                                                                                                         | OK<br>Cancel |

| Report File                                                                                                                                  |              |

| File Name: Report<br>Time Stamp<br>Separator<br>Comma<br>Tab<br>Space<br>Report File Update<br>New file on run<br>Keep exisiting file on run | Browse       |

| Display<br>Chart Type                                                                                                                        |              |

- **2** Set the time interval in which the display is to be updated. You can enter an *Update Interval* between **100** ... **7FFFFFFFh** milliseconds.

- **3** To get a file (\*.rtl) that contains all measurements results, check *Create Report File*. This allows you to specify further report options.

For more information on report options, please refer to *RTP Options Dialog Box* in the *Agilent E2929A/B Windows and Dialog Boxes User Interface Reference*.

4 Specify how the results are displayed:

Select the Chart Type:

- Bar Graph shows the results of the last measurement time interval.

- *History* shows the result history. This is useful to detect peaks.

### How to Run a Performance Measurement

After completing the setup, the real-time performance measurement can be started.

Performance measurements can only be run in online mode. Click *Go Online* in the *Mode* menu, if necessary.

**Running the Test** To run the test configuration, click either

- the Run icon  $\blacktriangleright$  in the tool bar, or

- *Run* in the File menu.

**Display Modes** This shows the results of the selected measurements per time interval.

• If you have selected *Bar Graph* in the RTP Options dialog box, the results are displayed as follows.

• If you have selected *History* in the RTP Options dialog box, the results are displayed as follows.

**Stop the Measurement** To stop the measurement, click the *Stop* button and close the window.

# Setting Up a PCI-X Performance Optimizer Test

All steps that are required to set up a PCI-X performance test with the Agilent E2929A/B Opt. 200 Performance Optimizer are introduced here. How to set up a test properly is explained here, but not the use of the different features as such. See *"Measuring System or Device Performance"* on page 47 for information on the features.

**NOTE** The features of the Performance Optimizer are only available if the Performance Optimizer option has been installed with the correct license key.

Basically, you can divide the setup process into two parts:

• The **hardware setup** usually needs to be done only once for every system under test. It is assumed that you already are familiar with the Agilent E2929A/B testcard. If you need more information about how to install the testcard in the system under test or how to connect it to the control PC, refer to the "Agilent E2929A/B PCI-X Getting Started Guide".

The additional steps required for the Performance Optimizer are described in *"Setting Up the Test Hardware" on page 38.*

• The **software setup** includes starting the Performance Optimizer once per test session—and the individually setting up for every test. Information on these steps is found in "*Preparing the Software for the Test*" on page 40.

## **Setting Up the Test Hardware**

| To evaluate a system's performance with the Agilent E2929A/B Opt. 200<br>Performance Optimizer, the Agilent E2929A/B testcard must be plugged<br>into the system under test. Refer to <i>Possible PCI-X Configurations</i> in<br>the <i>Getting Started Guide</i> for the different possible configurations.                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| If you wish to test a system's PCI-X performance but not the performance of a particular PCI-X device on the bus, your hardware setup is already finished with the installation of the testcard and the establishment of the connection to the control software. Proceed with <i>"Preparing the Software for the Test" on page 40</i> . |

| If, on the other hand, you want to evaluate the traffic of particular PCI-X devices, you need to allow the Performance Optimizer to identify requester and completer devices:                                                                                                                                                           |

| Requester devices                                                                                                                                                                                                                                                                                                                       |

| Requester devices initiate all read/write traffic on the PCI-X bus.<br>Requester devices are identified by their bus number, device number<br>and function number.                                                                                                                                                                      |

| How to specify the requester devices in the Performance Optimizer is described in <i>"Requester Identification"</i> on page 39.                                                                                                                                                                                                         |

| • Completer devices                                                                                                                                                                                                                                                                                                                     |

| Completer devices are devices addressed by a transaction. Thus, completer devices are identified by their address spaces.                                                                                                                                                                                                               |

| How to specify the completer devices and their address spaces is described in <i>"Completer Identification" on page 39</i>                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                         |

### **Requester Identification**

If you want to measure and evaluate the PCI-X traffic initiated by particular requester devices, you need to set up the Performance Optimizer to identify these requesters.

The requesters are specifically identified by their bus number, function number and device number.

The easiest way to find out which numbers the system under test assigns to the various requester devices is by running the performance measurement and viewing the report output. Section 1.1 of the report lists all requesters found on the bus and displays their corresponding bus, device and function numbers.

### **Completer Identification**

Every completer in a PCI-X system is assigned a unique address range during system startup. A completer may have several decoders and may, therefore, use several different address spaces at once. The PCI-X Performance Optimizer considers the different address spaces of such PCI-X devices as independent devices.

Basically, memory and I/O transactions can use the same addresses. Depending on the type of traffic to be examined, you can specify whether only memory commands, I/O commands, or both are to be evaluated by the PCI-X Performance Optimizer. See *"Preparing the Software for the Test" on page 40* for more information.

### **Preparing the Software for the Test**

This section covers all information needed to set up the Agilent E2929A/B Opt. 200 PCI-X Performance Optimizer. It is assumed that the required hardware has already been set up. If this is not the case, refer to *"Setting Up the Test Hardware" on page 38.*

The different steps of the software setup—except for the first one—can be done on the different tabs in the Performance Setup window of the GUI. This window can be opened either by selecting *Performance Setup* from the *Performance* menu or by clicking the Performance Setup button in the main window.

Steps of Software Setup The different steps of the software setup are:

- Requester Identification tab and Completer Identification tab In case you want to run performance measurements on particular PCI-X devices, you need to specify the respective requester and completer devices. See "Setting up the Completer Identification" on page 41 and "Setting up the Requester Identification" on page 42 for details.

- Pair Select tab

To restrict the performance test on a single device or a single requester-completer pair, see *"Selecting a Requester-Completer Pair"* on page 43 for instructions.

• Capture tab

Finally, to customize the start and end of the measurement period, you can specify trigger variables. See *"Setting Up the Data Capture" on page 44* for details.

### Setting up the Completer Identification

The PCI-X Performance Optimizer allows you to evaluate the performance of single PCI-X devices or communicating pairs of devices. The completer identification is used to specify the completer devices of interest. Every completer is identified by the address range that it decodes. You can monitor up to ten different completers at a time.

One completer device in a PCI-X system may have up to six completer decoders, each using its own address space. Within the Performance Optimizer they are regarded as independent completers.

To define the completer identification proceed as follows:

- 1 If the Performance window is not yet opened, click the Performance Setup button iii in the main window.

- 2 Select the Completer Identification tab.

| Performance Setur<br>Bun Help | )                    |                                         |                                         | _       |    |

|-------------------------------|----------------------|-----------------------------------------|-----------------------------------------|---------|----|

| <br>-<br>-<br>-               |                      |                                         |                                         |         |    |

| Report Completer Id           | lentification   Requ | ester Identification                    | Pair Select Cap                         | oture   |    |

|                               | Enter Ad             | Idress and Size for C                   | ompleters                               |         |    |

|                               | Completer Name       | Base Address                            | Size                                    | Command |    |

| Completer_1                   | Completer_1          | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 |         |    |

| Completer_2                   | Completer_2          | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 | NONE 🔺  |    |

| Completer_3                   | Completer_3          | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 | MEM     |    |

| Completer_4                   | Completer_4          | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 | ANY 🚽   |    |

| Completer_5                   | Completer_5          | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 | NONE    |    |

| Completer_6                   | Completer_6          | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 | NONE    |    |

| Completer_7                   | Completer_7          | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 | NONE .  | -1 |

- **3** If you wish to have a particular name for a completer in the report and displays, enter the name in *Completer Name*. The description of entering a name is an option.

- **4** Configure the completer by entering the following:

- The Base Address of the completer's memory.

- The ending  $\forall h$  marks hex values.

- The *Size* of the completer's memory.

The ending \h marks hex values.

- Which commands are to be used.

With this selection, you can restrict your measurements to traffic using either I/O commands or memory commands, or ignore it at all.

**5** Repeat the steps for all completers you want to be considered in the performance measurements.

### **Setting up the Requester Identification**

The requester identification is used for performance measurements on one or more particular requester devices. Every requester is identified by its bus, device and function number. You can monitor up to ten different requesters at a time.

To define the requester identification:

- 1 If the Performance window is not yet opened, click the Performance Setup button iii in the main window.

- 2 Select the Requester Identification tab.

| <u>R</u> un <u>H</u> elp |                       |                      |                   |          |   |

|--------------------------|-----------------------|----------------------|-------------------|----------|---|

| <b>B B</b>               |                       |                      |                   |          |   |

| oort Completer           | Identification Requ   | ester Identification | PairSelect C      | apture   |   |

|                          | Enter the Bus-, Devid | ce- and Functionnur  | mber of the Reque | sters    |   |

|                          | Requester Name        | Bus                  | Device            | Function |   |

| Requester_1              | Requester_1           | 0\h                  | 0\h               | 0\h      | - |

| Requester_2              | Requester_2           | 0\h                  | 0\h               | 0\h      |   |

| Requester_3              | Requester_3           | 0\h                  | 0\h               | 0\h      |   |

| Requester_4              | Requester_4           | 0\h                  | 0\h               | 0\h      |   |

| Requester_5              | Requester_5           | 0\h                  | 0\h               | 0\h      |   |

|                          | Requester_6           | 0\h                  | 0\h               | 0\h      |   |

| Requester_6              |                       |                      | 0\h               | 0\h      |   |

- **3** If you wish to have a particular name for a requester in the report and in the graphical displays, enter a *Requester Name*. The description of entering a name is an option.

- **4** Configure the requester by entering the following:

- The bus number in which the requester is located.

- The device number of this requester.

- The function number of this requester.

- **5** Repeat the steps for all requesters you want to be considered in the performance measurements.

### **Selecting a Requester-Completer Pair**

Besides the more general performance measurements for the specified PCI-X devices, the Performance Optimizer can also report detailed transaction statistics for a particular device or a communicating pair of devices.

To select a device or a pair of devices for the test:

- 1 If the Performance window is not yet opened, click the Performance Setup button 🔛 in the main window.

- 2 Select the *Pair Select* tab.

| 🖑 Performance Setup 📃 🗆 🗙                                                    |

|------------------------------------------------------------------------------|

| <u>File R</u> un <u>H</u> elp                                                |

|                                                                              |

| Report Completer Identification Requester Identification Pair Select Capture |

| Select the Requester Completer Pair you want to observe                      |

| Requester:                                                                   |

| Completer:                                                                   |

| Command Type: Read Write                                                     |

| Title:                                                                       |

- **3** From the *Requester* list and the *Completer* list select the combination of devices that you want to observe.

- **4** If you want to restrict your measurements to data transfers in one direction only, make the respective selection in the *Command Type* list.

The traffic direction is defined as seen from the requester's view. Thus, *Read* represents the traffic from completer to requester, and *Write* from requester to completer.

**5** If you want to specify a title that represents the device selection, enter a title in the *Title* text field. This title will then appear in the report and the output charts.

### **Setting Up the Data Capture**

For certain tests, it can be very useful to measure the performance during a particular period of time. Especially if you want to optimize or debug a PCI-X device, it is required to record the data traffic for postprocessed analysis only when certain events have occurred.

For purposes like this, it is possible to either delay the start of the test for a fixed time or to wait for a trigger event on the bus. Also, the end of the test can be set to a fixed number of recorded bus clocks or after an access to a certain address with a certain command.

To specify a trigger for a conditional start:

- 1 If the Performance window is not yet opened, click the Performance Setup button iii in the main window.

- **2** Select the *Capture* tab.

| Performance Setup                                                            |

|------------------------------------------------------------------------------|

| <u>Fi</u> le <u>R</u> un <u>H</u> elp                                        |

|                                                                              |

| Report Completer Identification Requester Identification Pair Select Capture |

| Trigger on                                                                   |

| TRUE Edit                                                                    |

|                                                                              |

|                                                                              |

| End of Analysis                                                              |

| Stop at end of Tracememory                                                   |

| C Stop after 0 samples                                                       |

| C Stop after access to address 0 with ID Read                                |

|                                                                              |

|                                                                              |

|                                                                              |

|                                                                              |

|                                                                              |

**3** Define the trigger in the *Trigger on* group by clicking on the *Edit* button.

The Capture window opens, where you can define the test to either start immediately or after the specified pattern was found to be true.

This window is part of the Agilent PCI-X Analyzer GUI and is not explained in detail here. If you need more information, please refer to *How to Set Up the Trigger* in the "*Agilent E2929A/B PCI-X Analyzer User's Guide*" Agilent.

- **4** Define the length of the test run in the *End of Analysis* group. The three possible options are:

- Stop at end of Tracememory (default)

With this option, the measurements continue until the complete trace memory is filled.

- Stop after ... samples

This option defines the test to stop after a certain number of recorded traffic samples. Specify the number of samples to record in the text field. This number must not be larger than the size of the trace memory.

A sequence of bus cycles without any signal changes concerning the performance (for example idle states) is stored as one sample. Thus, the number of observed bus cycles is larger than the number of samples in the trace memory.

- Stop after access to address ... with ...

The analysis stops after an access to the specified address with the specified PCI-X bus command. Enter the address in hex format in the text field and select a bus command from the list.

If the address or command does not occur on the bus, the test will run until the trace memory is filled completely.

If the measurements should run too long, you can always manually terminate the tests. The results presented then are calculated based on the completed test repetitions only.

**NOTE** If you store the waveform file after a repetitive test run, only the data of the most recent test will be stored. Later analysis of this file will possibly yield results other than the statistics on the complete set of tests.

## Measuring System or Device Performance

The Agilent E2929A/B Opt. 200 PCI-X Performance Optimizer can be used to measure the performance of a complete PCI-X system as well as to analyze particular PCI-X devices. The presented results and statistics allow you to debug the test devices and to optimize their performance in terms of data throughput, efficiency, bus utilization and split behavior.

After you have set up the test correctly (as described in *"Setting Up a PCI-X Performance Optimizer Test" on page 37*), you can run it and, when finished, examine the results in several different views.

- All information needed to run the performance measurements is found in "Running the Performance Measurements" on page 48.

- After the test is finished, the Performance Charts window presents the results. These charts are explained in "*Interpreting the Result Charts*" on page 49.

- An introduction to the contents of the performance report can be found in *"Interpreting the Report Output" on page 54.*

- An example of a performance report of a system evaluation test is explained in more detail in *"Using the Report Output for Performance Evaluation" on page 55.*

- Another example containing statistics on the data traffic of a particular device is found in *"Using the Report Output for Performance Optimization" on page 62.*

### **Running the Performance Measurements**

The Agilent E2929A/B PCI-X Performance Optimizer allows you to record detailed information on the bus traffic in the trace memory and evaluate it after the test is finished.

Assuming that the test was setup properly, the test will record bus traffic information in the trace memory for a certain amount of time. The length depends on the system speed and the size of the trace memory. The test can be controlled with several buttons found in the different windows of the Performance Optimizer—except the Performance Report window.

| Start the Test | To start the test, click the Run button in any of the windows of the |

|----------------|----------------------------------------------------------------------|

|                | Performance Optimizer. You can also select Run from the Performance  |

|                | menu in the main window.                                             |

Stop the TestIf for any reason your test does not seem to finish within a reasonable<br/>time, for example, if the specified trigger event does not occur, you can<br/>terminate it manually. Click the Stop button in either of the windows of<br/>the Performance Optimizer or select *Stop* from the Performance menu in<br/>the main window.

After the test is finished, the contents of the trace memory will be evaluated and the results will be presented in the Performance Charts window and the Performance Report window.

**Rescan the Trace Memory** The Rescan button is meant to be used when doing different performance calculations on the same data.